研讨会精华分享四 以成功率和可靠性为核心的纳米尺度集成电路设计方法学与软件开发

随着集成电路工艺节点不断向纳米乃至更小尺度演进,传统设计方法学正面临前所未有的挑战。在近期举办的“先进集成电路设计”系列研讨会上,第四场专题聚焦于“成功率和可靠性驱动的纳米尺度集成电路设计方法学与软件开发”,多位业界专家与学者分享了前沿洞见与实践经验。

一、 纳米尺度设计面临的严峻挑战

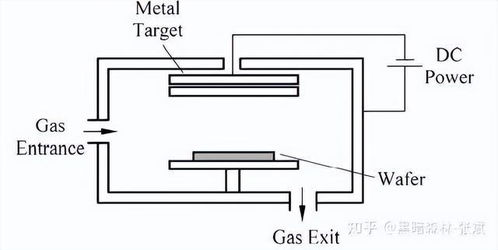

当特征尺寸进入深纳米领域(如7纳米、5纳米及以下),物理效应愈发显著。量子隧穿、工艺波动、电迁移、热效应以及更复杂的互连寄生参数等问题,使得设计首次成功率(First-Time Success Rate)急剧下降,芯片的长期可靠性也面临严峻考验。单纯追求性能与功耗指标的传统设计流程已难以满足需求,必须在设计初期就将制造成功率和长期可靠性作为核心驱动目标。

二、 成功率和可靠性驱动的设计方法学核心

新型方法学的核心在于将“可制造性设计”(DFM)和“可靠性设计”(DFR)理念深度融合,并前置到设计流程的每一个关键环节。

- 预测与建模先行:建立高精度的工艺与器件波动模型、老化模型(如BTI、HCI)、软错误率模型以及热模型。这些模型是进行早期分析和优化的基础。

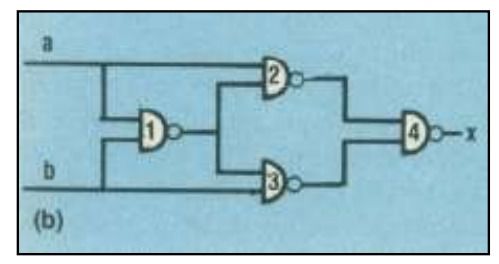

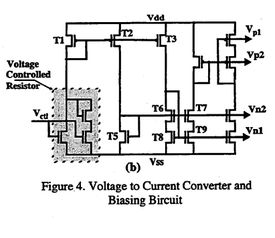

- 设计空间协同探索:在架构设计、逻辑综合、物理实现等阶段,工具需能够同时评估性能、功耗、面积(PPA)与良率、可靠性指标,实现多目标协同优化。

- 冗余与容错设计:在系统架构层面,明智地引入冗余设计(如ECC、冗余逻辑单元)和自适应调节机制(如动态电压频率调整DVFS),以容忍部分失效,提升系统级可靠性。

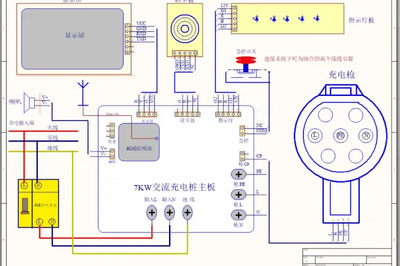

- 签核流程的强化:除了传统的时序、功耗签核外,必须引入并严格执行电迁移签核、热签核、可靠性签核(如老化分析)和制造良率签核,形成全面的“可靠性签核”闭环。

三、 支撑方法学的关键软件开发

先进的方法学离不开强大软件工具的支撑。相关软件开发呈现以下趋势:

- 智能化与自动化:利用机器学习(ML)和人工智能(AI)技术,从海量设计数据与制造数据中学习,快速预测设计热点、潜在故障点并自动生成优化方案,极大提升设计效率和成功率。例如,ML驱动的布局布线、良率预测和参数调优。

- 多物理场仿真集成:开发能够耦合电路、热、机械应力等多物理场效应的仿真平台,实现更真实的可靠性评估。

- 全流程数据管理与协同:建立统一的设计数据管理平台,确保从架构到制造的每一环节都能获取一致、准确的模型与约束信息,实现真正的“左移”(Shift-Left),让可靠性考量尽早介入。

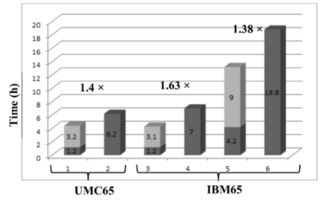

- 云原生与弹性计算:面对日益增长的计算复杂度(如蒙特卡洛分析、大规模参数扫描),设计工具正转向云原生架构,利用弹性计算资源并行处理,使原本耗时数周的分析能在数小时内完成。

四、 未来展望

专家们一致认为,面向更先进的工艺节点,成功率和可靠性将不再是设计流程末端的“检查项”,而是贯穿始终的“驱动力”。未来方法学与软件的演进,将更加强调系统-电路-工艺的协同优化(DTCO),以及借助人工智能实现设计范式的根本性变革。开源设计工具与生态的崛起,也为更多创新者参与这一关键领域提供了可能。

本次研讨会清晰地指出,唯有通过方法学的革新与软件工具的强力赋能,才能在纳米尺度集成电路设计的复杂迷宫中,开辟出一条通向高成功率、高可靠性的路径,支撑起下一代信息技术的坚实基础。

如若转载,请注明出处:http://www.iswapace.com/product/63.html

更新时间:2026-02-24 07:40:50